Time-to-digital converter

This article has multiple issues. Please help improve it or discuss these issues on the talk page. (Learn how and when to remove these template messages)

|

In electronic instrumentation and signal processing, a time-to-digital converter (TDC) is a device for recognizing events and providing a digital representation of the time they occurred. For example, a TDC might output the time of arrival for each incoming pulse. Some applications wish to measure the time interval between two events rather than some notion of an absolute time.

In electronics time-to-digital converters (TDCs) or time digitizers are devices commonly used to measure a time interval and convert it into digital (binary) output. In some cases [1] interpolating TDCs are also called time counters (TCs).

TDCs are used to determine the time interval between two signal pulses (known as start and stop pulse). Measurement is started and stopped when the rising or falling edge of a signal pulse crosses a set threshold. This pattern is seen in many physical experiments, like time-of-flight and lifetime measurements in atomic and high energy physics, experiments that involve laser ranging and electronic research involving the testing of integrated circuits and high-speed data transfer.[1]

Application

[edit]TDCs are used to timestamp events and measure time differences between events, especially where picosecond precision and high accuracy is required, such as the measurement of events in high energy physics experiments, where particles (e.g. electrons, photons, and ions) are detected.

Another application is cost-effective and non-mechanical water flow metering by measuring the time difference between ultrasound pulses that travel through the flow and arrive at different times depending on the flow speed and direction.[2][3]

In an all-digital phase-locked loop (ADPLL), a TDC measures the phase shift and its result is used to adjust the digital controlled oscillator (DCO).[4]

Coarse measurement

[edit]

If the required time resolution is not high, then counters can be used to make the conversion.

Basic counter

[edit]In its simplest implementation, a TDC is simply a high-frequency counter that increments every clock cycle. The current contents of the counter represents the current time. When an event occurs, the counter's value is captured in an output register.

In that approach, the measurement is an integer number of clock cycles, so the measurement is quantized to a clock period. To get finer resolution, a faster clock is needed. The accuracy of the measurement depends upon the stability of the clock frequency.

Typically a TDC uses a crystal oscillator reference frequency for good long term stability. High stability crystal oscillators are usually relative low frequency such as 10 MHz (or 100 ns resolution).[5] To get better resolution, a phase-locked loop frequency multiplier can be used to generate a faster clock. One might, for example, multiply the crystal reference oscillator by 100 to get a clock rate of 1 GHz (1 ns resolution).

Counter technology

[edit]High clock rates impose additional design constraints on the counter: if the clock period is short, it is difficult to update the count. Binary counters, for example, need a fast carry architecture because they essentially add one to the previous counter value. A solution is using a hybrid counter architecture. A Johnson counter, for example, is a fast non-binary counter. It can be used to count very quickly the low order count; a more conventional binary counter can be used to accumulate the high order count. The fast counter is sometime called a prescaler.

The speed of counters fabricated in CMOS-technology is limited by the capacitance between the gate and the channel and by the resistance of the channel and the signal traces. The product of both is the cut-off-frequency. Modern chip technology allows multiple metal layers and therefore coils with a large number of windings to be inserted into the chip. This allows designers to peak the device for a specific frequency, which may lie above the cut-off-frequency of the original transistor.[citation needed]

A peaked variant of the Johnson counter is the traveling-wave counter which also achieves sub-cycle resolution. Other methods to achieve sub-cycle resolution include analog-to-digital converters and vernier Johnson counters.[citation needed]

Measuring a time interval

[edit]

In most situations, the user does not want to just capture an arbitrary time that an event occurs, but wants to measure a time interval, the time between a start event and a stop event.

That can be done by measuring an arbitrary time of both the start and stop events and subtracting. The measurement can be off by two counts.

The subtraction can be avoided if the counter is held at zero until the start event, counts during the interval, and then stops counting after the stop event.

Coarse counters base on a reference clock with signals generated at a stable frequency .[1] When the start signal is detected the counter starts counting clock signals and terminates counting after the stop signal is detected. The time interval between start and stop is then

with , the number of counts and , the period of the reference clock.

Statistical counter

[edit]Since start, stop and clock signal are asynchronous, there is a uniform probability distribution of the start and stop signal-times between two subsequent clock pulses. This detuning of the start and stop signal from the clock pulses is called quantization error.

For a series of measurements on the same constant and asynchronous time interval one measures two different numbers of counted clock pulses and (see picture). These occur with probabilities

with the fractional part of . The value for the time interval is then obtained by

Measuring a time interval using a coarse counter with the averaging method described above is relatively time consuming because of the many repetitions that are needed to determine the probabilities and . In comparison to the other methods described later on, a coarse counter has a very limited resolution (1ns in case of a 1 GHz reference clock), but satisfies with its theoretically unlimited measuring range.

Fine measurement

[edit]In contrast to the coarse counter in the previous section, fine measurement methods with much better accuracy but far smaller measuring range are presented here.[1] Analogue methods like time interval stretching or double conversion as well as digital methods like tapped delay lines and the Vernier method are under examination. Though the analogue methods still obtain better accuracies, digital time interval measurement is often preferred due to its flexibility in integrated circuit technology and its robustness against external perturbations like temperature changes.

The counter implementation's accuracy is limited by the clock frequency. If time is measured by whole counts, then the resolution is limited to the clock period. For example, a 10 MHz clock has a resolution of 100 ns. To get resolution finer than a clock period, there are time interpolation circuits.[6] These circuits measure the fraction of a clock period: that is, the time between a clock event and the event being measured. The interpolation circuits often require a significant amount of time to perform their function; consequently, the TDC needs a quiet interval before the next measurement.

Ramp interpolator

[edit]When counting is not feasible because the clock rate would be too high, analog methods can be used. Analog methods are often used to measure intervals that are between 10 and 200 ns.[7] These methods often use a capacitor that is charged during the interval being measured.[8][9][10][11] Initially, the capacitor is discharged to zero volts. When the start event occurs, the capacitor is charged with a constant current I1; the constant current causes the voltage v on the capacitor to increase linearly with time. The rising voltage is called the fast ramp. When the stop event occurs, the charging current is stopped. The voltage on the capacitor v is directly proportional to the time interval T and can be measured with an analog-to-digital converter (ADC). The resolution of such a system is in the range of 1 to 10 ps.[12]

Although a separate ADC can be used, the ADC step is often integrated into the interpolator. A second constant current I2 is used to discharge the capacitor at a constant but much slower rate (the slow ramp). The slow ramp might be 1/1000 of the fast ramp. This discharge effectively "stretches" the time interval;[13] it will take 1000 times as long for the capacitor to discharge to zero volts. The stretched interval can be measured with a counter. The measurement is similar to a dual-slope analog converter.

The dual-slope conversion can take a long time: a thousand or so clock ticks in the scheme described above. That limits how often a measurement can be made (dead time). Resolution of 1 ps with a 100 MHz (10 ns) clock requires a stretch ratio of 10,000 and implies a conversion time of 150 μs.[13] To decrease the conversion time, the interpolator circuit can be used twice in a residual interpolator technique.[13] The fast ramp is used initially as above to determine the time. The slow ramp is only at 1/100. The slow ramp will cross zero at some time during the clock period. When the ramp crosses zero, the fast ramp is turned on again to measure the crossing time (tresidual). Consequently, the time can be determined to 1 part in 10,000.

Interpolators are often used with a stable system clock. The start event is asynchronous, but the stop event is a following clock.[9][11] For convenience, imagine that the fast ramp rises exactly 1 volt during a 100 ns clock period. Assume the start event occurs at 67.3 ns after a clock pulse; the fast ramp integrator is triggered and starts rising. The asynchronous start event is also routed through a synchronizer that takes at least two clock pulses. By the next clock pulse, the ramp has risen to .327 V. By the second clock pulse, the ramp has risen to 1.327 V and the synchronizer reports the start event has been seen. The fast ramp is stopped and the slow ramp starts. The synchronizer output can be used to capture system time from a counter. After 1327 clocks, the slow ramp returns to its starting point, and interpolator knows that the event occurred 132.7 ns before the synchronizer reported.

The interpolator is actually more involved because there are synchronizer issues and current switching is not instantaneous.[14] Also, the interpolator must calibrate the height of the ramp to a clock period.[15]

Vernier

[edit]Vernier interpolator

[edit]The vernier method is more involved.[16] The method involves a triggerable oscillator[17] and a coincidence circuit. At the event, the integer clock count is stored and the oscillator is started. The triggered oscillator has a slightly different frequency than the clock oscillator. For sake of argument, say the triggered oscillator has a period that is 1 ns faster than the clock. If the event happened 67 ns after the last clock, then the triggered oscillator transition will slide by −1 ns after each subsequent clock pulse. The triggered oscillator will be at 66 ns after the next clock, at 65 ns after the second clock, and so forth. A coincidence detector looks for when the triggered oscillator and the clock transition at the same time, and that indicates the fraction time that needs to be added.

The interpolator design is more involved. The triggerable clock must be calibrated to clock. It must also start quickly and cleanly.

Vernier method

[edit]The Vernier method is a digital version of the time stretching method. Two only slightly detuned oscillators (with frequencies and ) start their signals with the arrival of the start and the stop signal. As soon as the leading edges of the oscillator signals coincide the measurement ends and the number of periods of the oscillators ( and respectively) lead to the original time interval :

Since highly reliable oscillators with stable and accurate frequency are still quite a challenge one also realizes the vernier method via two tapped delay lines using two slightly different cell delay times . This setting is called differential delay line or vernier delay line.[18]

In the example presented here the first delay line affiliated with the start signal contains cells of D-flip-flops with delay which are initially set to transparent. During the transition of the start signal through one of those cells, the signal is delayed by and the state of the flip-flop is sampled as transparent. The second delay line belonging to the stop signal is composed of a series of non-inverting buffers with delay . Propagating through its channel the stop signal latches the flip-flops of the start signal's delay line. As soon as the stop signal passes the start signal, the latter is stopped and all leftover flip-flops are sampled opaque. Analogous to the above case of the oscillators the wanted time interval is then

with n the number of cells marked as transparent.

Digital Delay-Line based TDC

[edit]

In general a digital delay-line based TDC,[19] also known as tapped delay line, contains a chain of cells (e.g. using D-latches in the figure) with well defined delay times . The start signal propagates through this chain and is successively delayed by each cell. The number of cells that the start signal propagated through when the stop signal happens will be the (rounded) time interval between the start and stop signal divided by .

Hybrid measurement

[edit]

Counters can measure long intervals but have limited resolution. Interpolators have high resolution but they cannot measure long intervals. A hybrid approach can achieve both long intervals and high resolution.[1] The long interval can be measured with a counter. The counter information is supplemented with two time interpolators: one interpolator measures the (short) interval between the start event and a following clock event, and the second interpolator measure the interval between the stop event and a following clock event. The basic idea has some complications: the start and stop events are asynchronous, and one or both might happen close to a clock pulse. The counter and interpolators must agree on matching the start and end clock events. To accomplish that goal, synchronizers are used.

The common hybrid approach is the Nutt method.[20] In this example the fine measurement circuit measures the time between start and stop pulse and the respective second nearest clock pulse of the coarse counter (Tstart, Tstop), detected by the synchronizer (see figure). Thus the wanted time interval is

with n the number of counter clock pulses and T0 the period of the coarse counter.

History

[edit]Time measurement has played a crucial role in the understanding of nature from the earliest times. Starting with sun, sand or water driven clocks we are able to use clocks today, based on the most precise caesium resonators.

The first direct predecessor of a TDC was invented in the year 1942 by Bruno Rossi for the measurement of muon lifetimes.[21] It was designed as a time-to-amplitude-converter, constantly charging a capacitor during the measured time interval. The corresponding voltage is directly proportional to the time interval under examination.

While the basic concepts (like Vernier methods (Pierre Vernier 1584-1638) and time stretching) of dividing time into measurable intervals are still up-to-date, the implementation changed a lot during the past 50 years. Starting with vacuum tubes and ferrite pot-core transformers those ideas are implemented in complementary metal–oxide–semiconductor (CMOS) design today.[22]

Errors

[edit]- Some information from [1]

Regarding even the fine measuring methods presented, there are still errors one may wish remove or at least to consider. Non-linearities of the time-to-digital conversion for example can be identified by taking a large number of measurements of a poissonian distributed source (statistical code density test).[23] Small deviations from the uniform distribution reveal the non-linearities. Inconveniently the statistical code density method is quite sensitive to external temperature changes. Thus stabilizing delay or phase-locked loop (DLL or PLL) circuits are recommended.

In a similar way, offset errors (non-zero readouts at T = 0) can be removed.

For long time intervals, the error due to instabilities in the reference clock (jitter) plays a major role. Thus clocks of superior quality are needed for such TDCs.

Furthermore, external noise sources can be eliminated in postprocessing by robust estimation methods.[24]

Configurations

[edit]TDCs are currently built as stand-alone measuring devices in physical experiments or as system components like PCI cards. They can be made up of either discrete or integrated circuits.

Circuit design changes with the purpose of the TDC, which can either be a very good solution for single-shot TDCs with long dead times or some trade-off between dead-time and resolution for multi-shot TDCs.

Delay generator

[edit]

The time-to-digital converter measures the time between a start event and a stop event. There is also a digital-to-time converter or delay generator. The delay generator converts a number to a time delay. When the delay generator gets a start pulse at its input, then it outputs a stop pulse after the specified delay. The architectures for TDC and delay generators are similar. Both use counters for long, stable, delays. Both must consider the problem of clock quantization errors.

For example, the Tektronix 7D11 Digital Delay uses a counter architecture.[25] A digital delay may be set from 100 ns to 1 s in 100 ns increments. An analog circuit provides an additional fine delay of 0 to 100 ns. A 5 MHz reference clock drives a phase-locked loop to produce a stable 500 MHz clock. It is this fast clock that is gated by the (fine-delayed) start event and determines the main quantization error. The fast clock is divided down to 10 MHz and fed to main counter.[26] The instrument quantization error depends primarily on the 500 MHz clock (2 ns steps), but other errors also enter; the instrument is specified to have 2.2 ns of jitter. The recycle time is 575 ns.

Just as a TDC may use interpolation to get finer than one clock period resolution, a delay generator may use similar techniques. The Hewlett-Packard 5359A High Resolution Time Synthesizer provides delays of 0 to 160 ms, has an accuracy of 1 ns, and achieves a typical jitter of 100 ps.[27] The design uses a triggered phase-locked oscillator that runs at 200 MHz. Interpolation is done with a ramp, an 8-bit digital-to-analog converter, and a comparator. The resolution is about 45 ps.

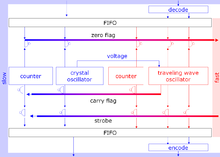

When the start pulse is received, then counts down and outputs a stop pulse. For low jitter the synchronous counter has to feed a zero flag from the most significant bit down to the least significant bit and then combine it with the output from the Johnson counter.

A digital-to-analog converter (DAC) could be used to achieve sub-cycle resolution, but it is easier to either use vernier Johnson counters or traveling-wave Johnson counters.

The delay generator can be used for pulse-width modulation, e.g. to drive a MOSFET to load a Pockels cell within 8 ns with a specific charge.

The output of a delay generator can gate a digital-to-analog converter and so pulses of a variable height can be generated. This allows matching to low levels needed by analog electronics, higher levels for ECL and even higher levels for TTL. If a series of DACs is gated in sequence, variable pulse shapes can be generated to account for any transfer function.

See also

[edit]References

[edit]- ^ a b c d e f Kalisz, Józef (February 2004), "Review of methods for time interval measurements with picosecond resolution", Metrologia, 41 (1), Institute of Physics Publishing: 17–32, Bibcode:2004Metro..41...17K, doi:10.1088/0026-1394/41/1/004, S2CID 250775541

- ^ Kris Ardis (2019-02-06). Maxim Integrated Application Note 5968 (Welcoming water metering into the 21st century) (PDF) (Technical report). Analog Devices.

- ^ Ultrasonic Flow Converters Application Note 023. Ultrasonic Water & Heat Metering with TDC-GP22 (PDF) (Technical report). ams AG. 2013-07-10.

- ^ Henzler, Stephan (2010). "6.1 Digital Phase Locked Loop". Time-to-Digital Converters. Springer Series in Advanced Microelectronics. Vol. 29. Dordrecht: Springer Netherlands. pp. 112–116. doi:10.1007/978-90-481-8628-0. ISBN 978-90-481-8627-3. ISSN 1437-0387.

- ^ For example, a Hewlett-Packard (now Agilent) 10811 crystal oven oscillator; http://www.hparchive.com/Manuals/HP-10811AB-Manual.pdf

- ^ Time and Frequency from A to Z, National Institute of Standards and Technology,

For example, multiplying the time base frequency to 100 MHz makes 10 ns resolution possible, and 1 ns counters have even been built using a 1 GHz time base. However, a more common way to increase resolution is to detect parts of a time base cycle through interpolation and not be limited by the number of whole cycles. Interpolation has made 1 ns TICs commonplace, and even 20 picosecond TICs are available.

, entry for time interval counter. - ^ Kalisz 2004, p. 19

- ^ Reeser, Gilbert A. (May 1969), "An Electronic Counter for the 1970's" (PDF), Hewlett-Packard Journal, 20 (9), Hewlett-Packard: 9–12

- ^ a b Sasaki, Gary D.; Jensen, Ronald C. (September 1980), "Automatic Measurements with a High Performance Universal Counter" (PDF), Hewlett-Packard Journal, 31 (9), Hewlett-Packard: 21–31

- ^ Rush, Kenneth; Oldfield, Danny J. (April 1986), "A Data Acquisition System for a 1-GHz Digitizing Oscilloscope", Hewlett-Packard Journal, 37 (4), Hewlett-Packard: 4–11

- ^ a b Eskeldson, David D.; Kellum, Reginald; Whiteman, Donald A. (October 1993), "A Digitizing Oscilloscope Time Base and Trigger System Optimized for Throughput and Low Jitter", Hewlett-Packard Journal, 44 (5), Hewlett-Packard: 21–30

- ^ Kalisz 2004, p. 20. Kalisz states that the Stanford Research Systems SR620 uses this method.

- ^ a b c Eskeldson, Kellum & Whiteman 1993, p. 27 stating, "Effectively, the interpolator magnifies the interpolation or uncertainty interval by the ratio of the charge and discharge currents."

- ^ Eskeldson, Kellum & Whiteman 1993, p. 27

- ^ Sasaki & Jensen 1980, p. 23 stating, "In practice, the current sources and other circuitry used to build the interpolators are subject to operational variations over temperature and time. The 5360A's interpolators were in a special insulated cavity and had several adjustments. The 5335A uses a self-calibration technique that is not affected by temperature and needs no adjustments."

- ^ Chu, David C.; Allen, Mark S.; Foster, Allen S. (August 1978), "Universal Counter Resolves Picoseconds in Time Interval Measurements" (PDF), HP Journal, 29 (12), Hewlett-Packard: 2–11

- ^ Chu, David C. (August 1978), "The Triggered Phase-Locked Oscillator" (PDF), HP Journal, 29 (12), Hewlett-Packard: 8–9

- ^ Henzler, Stephan (2010). "5.3 Vernier TDC". Time-to-Digital Converters. Springer Series in Advanced Microelectronics. Vol. 29. Dordrecht: Springer Netherlands. pp. 83–85. doi:10.1007/978-90-481-8628-0. ISBN 978-90-481-8627-3. ISSN 1437-0387.

- ^ Henzler, Stephan (2010). "2.4 Basic Digital Delay-Line Based TDC". Time-to-Digital Converters. Springer Series in Advanced Microelectronics. Vol. 29. Dordrecht: Springer Netherlands. pp. 22–26. doi:10.1007/978-90-481-8628-0. ISBN 978-90-481-8627-3. ISSN 1437-0387.

- ^ Kalisz, J.; Pawlowski, M.; Pelka, R. (1987), "Error analysis and design of the Nutt time-interval digitiser with picosecond resolution", J. Phys. E: Sci. Instrum., 20 (11): 1330–1341, Bibcode:1987JPhE...20.1330K, doi:10.1088/0022-3735/20/11/005

- ^ "Bruno Benedetto Rossi", George W. Clark, National Academic Press, Washington D.C. 1998, S.13

- ^ "Noise Shaping Techniques for Analog and Time to Digital Converters Using Voltage Controlled Oscillators", Matthew A.Z. Straayer, Phd-Thesis, Massachusetts Institute of Technology (2008)

- ^ Pelka, R.; Kalisz, J.; Szplet, R. (1997), "Nonlinearity correction of the integrated time-to-digital converter with direct coding", IEEE Transactions on Instrumentation and Measurement, 46 (2): 449–452, Bibcode:1997ITIM...46..449P, doi:10.1109/19.571882

- ^ Kalisz, J.; Pawlowski, M.; Pelka, R. (March 1994), "Precision time counter for laser ranging to satellites", Rev. Sci. Instrum., 65 (3): 736–741, Bibcode:1994RScI...65..736K, doi:10.1063/1.1145094

- ^ Tektronix 7D11 Digital Delay Service Instruction Manual, Beaverton, OR: Tektronix, 1973, 070-1377-01

- ^ Ten megahertz is a frequency that TTL logic in 1971 could handle. The high frequency divisions were handled with different technologies because high speed digital counters were uncommon in 1971. The first (500 MHz) divider stage is a 100 MHz synchronized multivibrator to effect a divide by 5 circuit. The second (100 MHz) stage is a divide by 5 ring counter made from discrete emitter-coupled transistors. The last stage is a flip-flop.

- ^ Ferguson, Keith M.; Dickstein, Leonard R. (August 1978), "Time Synthesizer Generates Precise Pulse Widths and Time Delays for Critical Timing Applications" (PDF), HP Journal, 29 (12): 12–19

External links

[edit]- US 3983481, Nutt, Ronald; Milam, Kelly & Williams, Charles W., "Digital intervalometer", published 4 August 1975, issued 18 September 1976

- US 3133189, Bagley, Alan S. & Brooksby, Merrill W., "Electronic Interpolating Counter for the Time Interval and Frequency Measurement", published 5 August 1960, issued 12 May 1964

- US 2665411, Frady, William E., Jr., "Double Interpolation Method and Apparatus for Measuring Time Intervals", published 15 March 1951, issued 5 January 1954

- US 2665410, Burbeck, Donald W., "Method and Apparatus for Automatically Measuring Time Intervals", published 15 March 1951, issued 5 January 1954

- US 2560124, Mofenson, Jack, "Interval Measuring System", published 31 March 1950, issued 10 July 1951

- US 8324952, Masters, Lewis W., "Time interpolator circuit", published 2012-12-04, issued 2011-05-04

- Le Grand de Mercey, G. "A 18GHz rotary traveling wave VCO in CMOS with I/Q outputs" (PDF). ESSCIRC 2004 - 29th European Solid-State Circuits Conference (IEEE Cat. No.03EX705). IEEE. doi:10.1109/esscirc.2003.1257179. Archived from the original (PDF) on 2011-07-09.

- Bhattacharyya, K.; Szymanski, T.H. "1.2 V CMOS 1-10 GHz traveling wave amplifiers using coplanar waveguides as on-chip inductors" (PDF). Proceedings. 2004 IEEE Radio and Wireless Conference (IEEE Cat. No.04TH8746). IEEE. doi:10.1109/rawcon.2004.1389112.

- John Ackermann (2020-11-28). "The HP 5370B Time Interval Counter [application notes and measured performance]". Retrieved 2023-09-26.

- "Data sheets, manuals and application notes on [mainly HP] time-interval counters". 2017-03-16. Archived from the original on 2017-03-16. Retrieved 2017-03-16.

- Yu. Artyukh; V. Bespal'ko; E. Boole. High Resolution Modular Time Interval Counter (PDF) (Technical report). Retrieved 2002-12-04.

- Fundamentals of Time Interval Measurements (Application Note 200-3) (PDF) (Technical report). Electronic Counter Series. HP.

- Zhang, Victor S.; Davis, Dick D.; Lombardi, Michael A. (1994-12-01). High Resolution Time Interval Counter (PDF). The 26th Annual Precise Time and Time Interval (PTTI) Applications and Planning Meeting. Defense Technical Information Center/NASA. Bibcode:1995ptti.meet..191Z.

- Salvatore, Loffredo (2010), Design, construction and tests of a high resolution, high dynamic range Time to Digital Converter Università degli studi Roma Tre, Scuola Dottorale in Scienze Matematiche e Fisiche

- Kalisz, Jozef; Szplet, Ryszard; Pelka, Ryszard (August 1997), "Single-Chip Interpolating Time Counter with 200-ps Resolution and 43-s Range", IEEE Transactions on Instrumentation and Measurement, 46 (4), IEEE: 851–856, Bibcode:1997ITIM...46..851K, doi:10.1109/19.650787, ISSN 0018-9456

- TDC7200 Time-to-Digital Converter for Time-of-Flight Applications in LIDAR, Magnetostrictive and Flow Meters [Datasheet] (PDF) (Technical report). TI. 2016-03-01.

French

French Deutsch

Deutsch